本篇目录:

verilog中有哪几种类型的赋值语句,说明它们的区别,并举例

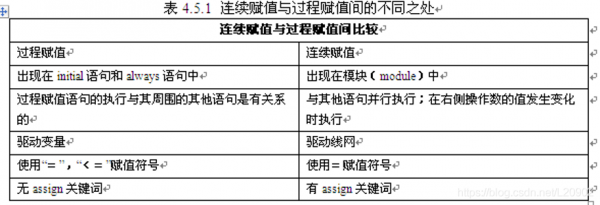

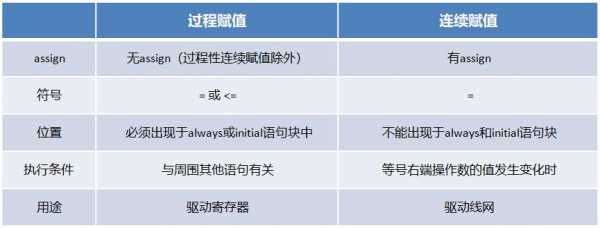

1、Verilog HDL 中赋值语句分“assign”连续赋值语句和过程赋值语句(阻塞赋值语句和非阻塞赋值语句在)。 连续赋值操作取决于表达式右侧变量是否变化,只要右侧变化,就会进行赋值操作;主要用于端口变量的赋值,也可用在组合逻辑的行为描述中。

2、reg:寄存器类型,数据存储单元,默认初始值为X。只能在always和intial语句中被赋值。

3、在always语句块中,verilog语言支持两种类型的赋值:阻塞赋值和非阻塞赋值。阻塞赋值使用“=”语句;非阻塞赋值使用“=”语句。

4、可简单的认为并列执行;而过程赋值语句,在initial块中,过程性赋值只顺序执行一次,而在always块中,每一次满足always的条件时,都要顺序执行一次该always块中的语句,可简单的认为过程赋值是按顺序执行的。

5、阻塞赋值:在Verilog HDL的概念中阻塞赋值操作符用等号(即=)表示。非阻塞赋值:非阻塞赋值操作符用小于等于号(即=)表示。

易语言数组如何进行连续赋值?

1、下载文件:利用取标记组件批量赋值.e|先对每个标签属性中的标志进行填写,然后再用取标志组件命令来批量赋值,很简单,4行代码就完成。

2、再请教一个问题,一行能否写多行语句,用啥号分开,一行语句在两行写完怎么连接,用的连接符号是什么?可能对你不是问题,对我是一个坎。 追答 易语言不支持多行写成一行,也不支持很长的一行代码拆成多行写。

3、你需要什么样子的赋值?同样的类型才可以同样的赋值。

C语言可以连续赋值么?如c=a=b=5???说详细哦

可以连续赋值。c=x(x:a=b=5)时,因为=的结合性从右到左,所以先计算x的值,计算x的值的时候发现x=y(y:b=5),所以需要先计算y的值,计算y的值的时候发现y=z(z:5),所以需要先计算z的值。

可以 。例如:c=a=b=5;这条语句是没有错误的,首先可以了解到‘=’作为一个运算符,它有从右至左的结合性。

可以 。int a , b , c ;a = b = c = 5 ; // 这样可以。但是 int a = b = c = 5 ; // 这样不可以,因为 b 跟 c 都还没有定义。

在变量说明中,不允许连续给多个变量赋初值。如下述说明是错误的:inta=b=c=5必须写为inta=5,b=5,c=5;而赋值语句允许连续赋值。赋值语句 将确定的数值赋给变量的语句叫做赋值语句。

在C语言中也可以组成赋值语句,按照C语言规定,任何表达式在其未尾加上分号就构成为语句。因此如x=8;a=b=c=5;都是赋值语句,在前面各例中我们已大量使用过了。

到此,以上就是小编对于过程赋值语句 连续赋值语句的问题就介绍到这了,希望介绍的几点解答对大家有用,有任何问题和不懂的,欢迎各位老师在评论区讨论,给我留言。

微信扫一扫打赏

微信扫一扫打赏