本篇目录:

- 1、揭秘集成电路设计之数字IC后端攻城狮

- 2、为什么cts报告中时钟从负值开始

- 3、时钟树综合的目标

- 4、时钟树延迟如何影响时间

- 5、数字后端——低功耗设计物理实施

- 6、IC设计前端到后端的流程和eda工具

揭秘集成电路设计之数字IC后端攻城狮

数字IC后端攻城狮 数字IC后端工程师是芯片微观界的建筑师,负责将前端工程师的设计图纸转化为实际的电路结构,并生成符合生产厂家要求的GDS文件。

后边是我要说明的,在集成电路设计中,分数字和模拟。模拟电路分前端(circuit design,电路设计)、后端(layout,版图)。数字电路也分前端(一般是算法和代码),后端(数字电路的后端就是布局布线)。

要一步步的自学数字集成电路设计需要:1,要学会半导体物理,拉扎维或者艾伦,然后看对应数字ic设计或者模拟ic设计的书,最后是版图。2,下载学习的软件maxplus或者quartus。

为什么cts报告中时钟从负值开始

因为定时器是加1运行的,当从255变到0时表示定时时间到,所以要用负数。例如,-2就是254,当2个定时脉冲后定时时间到。

是的。在定时器开始工作后,定时值不断递减,递减到零时,表示时间已到,定时器会有相应的动作,电子时钟plc设计中定时只能从零开始使用。时基是时间基准的简称。

为了防止clock上的SI和EM,我们需要对时钟信号线进行non-default rule的设置。通常设置两倍宽度,两倍间距(当然也有更大,根据实际情况进行更改)。

时钟树综合的目标

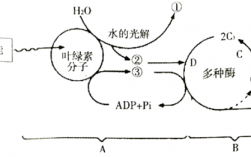

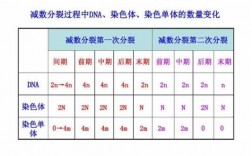

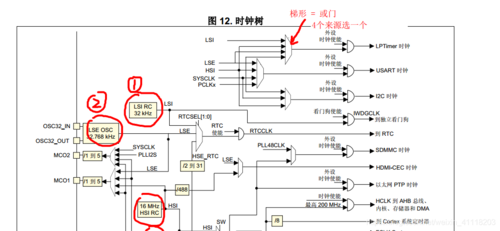

1、时钟树综合(Clock Tree Synthesis)一直是数字后端实现中最为重要的步骤之一。随着芯片时钟越来越多,设计阶段都采用了时钟切换电路,时钟结构越来越复杂(除了func mode外,还有test mode和mbist等模式)。

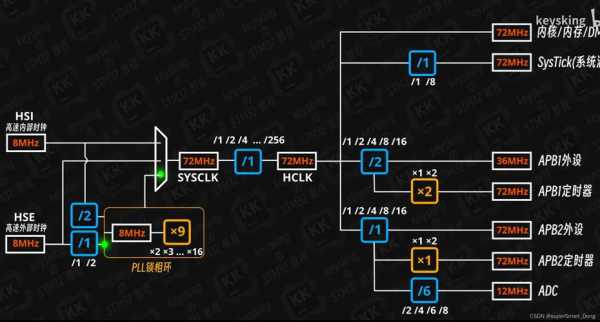

2、时钟树综合就是指从某个clock的root点长到各个sink点的clock buffer/inverter tree。工具试图将某个clock所属的所有sinks做到相同长度。从概念上,我们可以得到几个要点。

3、RTL逻辑综合的主要目标包括优化时序、功耗和面积。在物理实施阶段,同样需要优化芯片的总面积和芯核面积,这样可以进一步减小功耗。

4、Custom时钟树综合 对于简单的设计,可能clock_opt -cts或者ccopt_design -cts就可以把tree做的很好。但是对于复杂时钟结构的SOC设计,我们能否直接执行命令做Tree呢?显然是不能的。

时钟树延迟如何影响时间

1、**负载**:电路的负载也会影响时钟延迟。例如,如果电路上有大量的逻辑门或晶体管,那么时钟延迟可能会增加。 **电源质量**:电源质量,如电源层之间的阻抗,可能会影响时钟信号的延迟和质量。

2、在设计中插入延迟单元可以增加线的延迟,延迟单元是一种特殊的逻辑门,可以通过调整其参数来控制延迟时间。时钟树的布线和优化对于信号传输的延迟也有影响,通过调整时钟树的布线方式和参数,可以间接地影响线的延迟。

3、导致duty cycle出问题的主要原因是cell的rise delay和fall delay不平衡。因此,在做CTS综合时,我们往往都是用clock inverter 来做时钟树的。

4、对于慢速设计,时钟树的skew和latency对时序收敛的影响重要性下降。但是对于skew大的时钟树,工具修复时序会增加更多的面积和功耗。

数字后端——低功耗设计物理实施

在当下,为了节省功耗,各位工程师也是拼了。在后端实现的不断调整和改变的同时,前端的TX们也没有闲着。DVFS就是一个基于设计,功能原理的有效降低功耗的一个典型方案。

为了实现集成电路的低功耗设计目标,我们需要在系统设计阶段就采用低功耗设计的方案。而且,随着设计流程的逐步推进,到了芯片后端设计阶段,降低芯片功耗的方法已经很少了,节省的功耗百分比也不断下降。

数字IC后端攻城狮 数字IC后端工程师是芯片微观界的建筑师,负责将前端工程师的设计图纸转化为实际的电路结构,并生成符合生产厂家要求的GDS文件。

模拟后端和数字后端的区别是。前端设计也称逻辑设计和后端设计也称物理设计。并没有统一严格的界限,涉及到与工艺有关的设计就是后端设计。数字后端以布局布线为起点,以生成可以可以送交foundry进行流片的GDS2文件为终点。

要一步步的自学数字集成电路设计需要:1,要学会半导体物理,拉扎维或者艾伦,然后看对应数字ic设计或者模拟ic设计的书,最后是版图。2,下载学习的软件maxplus或者quartus。

IC设计前端到后端的流程和eda工具

设计输入 设计输入是将所设计的系统或电路以开发软件要求的某种形式表示出来,并输入给EDA工具的过程。常用的方法有硬件描述语言(HDL)和原理图输入方法等。

现代数字系统的设计流程是指利用EDA开发软件和编程工具对可编程逻辑器件进行开发的过程。在EDA软件平台上,利用硬件描述语言HDL等逻辑描述手段完成设计。

如果有机会参加一些有很好设计背景的人做的培训,最好是互动式的,也会有较好的收获。

一般来说,数字IC后端工程师会和模拟IC前端设计人员、厂家技术人员、封装测试技术人员频繁对接。

芯片设计两大流程 前面说的芯片前端设计,又可细分为行为级、RTL级、门级,行为级描述电路功能,RTL级描述电路结构,门级描述门这一级电路的结构。

到此,以上就是小编对于时钟树的时钟源有哪几个,分别是多少hz?的问题就介绍到这了,希望介绍的几点解答对大家有用,有任何问题和不懂的,欢迎各位老师在评论区讨论,给我留言。

微信扫一扫打赏

微信扫一扫打赏